纳米(nm)是一个长度单位,经常出现在芯片制程上,如:麒麟990是7nm技术,麒麟9000是5nm技术,三星和台积电争夺3nm技术等等。

那么所谓的7nm、5nm、究竟有多长呢?它是指芯片哪一部分的长度呢?真的是越小越先进吗?我们一起来看一看。

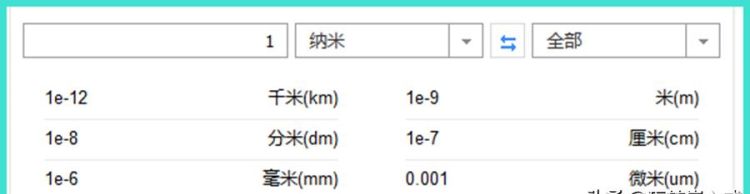

纳米究竟有多长

纳米,即为毫微米,是长度的度量单位,国际单位制符号为nm。

1nm有多长呢?

1nm=0.000000001米=10^(-9)米。1nm=4个原子大小。而原子是化学反应中最小的微粒,肉眼无法看到。

如果把一根头发平均分成5万份,那么每一份的厚度就是1nm。

由于纳米的特殊性,也演变出了纳米技术,芯片技术也属于纳米技术的范畴。

纳米技术也称豪微米技术,是研究尺寸在1纳米至100纳米范围内的材料应用技术,而这个尺寸范围基本是原子、分子、超分子级别的,因此又被称为分子纳米技术。

纳米技术主要分为三大类:

- 纳米机器人,把机器人做到微小化,达到纳米的级别,机器人可以任意组合分子,就像搭积木一样。这种概念的纳米技术还未取得重大进展。

- 纳米加工技术,主要应用在半导体制造领域,技术已经成熟,目前已经量产了5nm工艺的芯片,典型代表有:台积电技术的苹果A14、麒麟9000,三星技术的骁龙888。

- 生物纳米技术,是从生物学的角度出发而提出的。在细胞和生物膜内就存在纳米级的结构。而这种技术,可以促进DNA分子计算机、细胞生物计算机的开发,形成纳米生物技术。

随着技术的发展,纳米技术的应用会越来越广泛,芯片制造工艺也会越来越精细。纳米科学技术也会引领新的科学技术,如:纳米化学、纳米电子学、纳米物理学、纳米生物学等。

制程(纳米)在芯片中究竟是怎么回事?

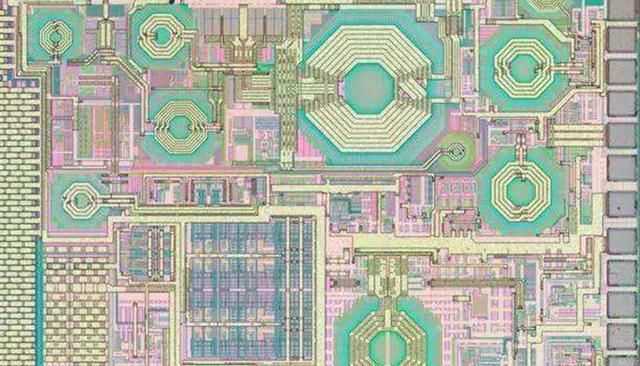

芯片又称集成电路,是美国仙童公司Robert Noyce与德州仪器基尔比发明的,最开始的芯片是把晶体管、电阻、电阻等集成在一个很小的平板上,然后用很细的线把这些元器件连接起来,实现了最简单的芯片功能。

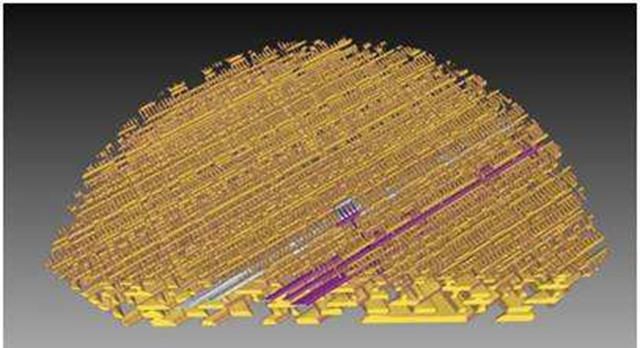

随着芯片技术不断地发展,现在的芯片已经可以集成上百亿的晶体管,实现超级计算功能。而制造工艺也达到了5nm制程。

很多网友认为这个工艺制程5nm是晶体管长度,其实并非如此。那么这5nm制程究竟是指的芯片的哪个部位呢?

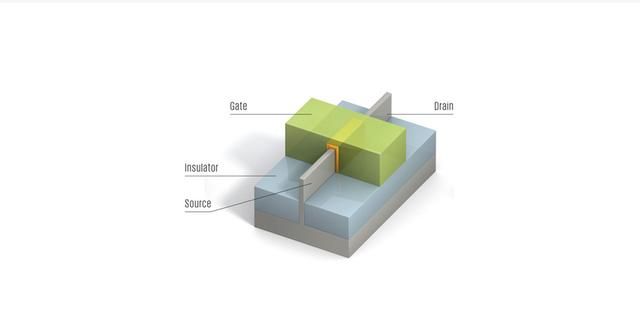

在晶体管结构中,电流从Source(源极)流入Drain(漏级),Gate(栅极)相当于闸门,主要负责控制两端源极和漏级的通断。而栅极的最小宽度(栅长),就是这个工艺制程5nm。

那么如何才能把更多的晶体管放到有限的芯片中呢?

那就是缩小芯片中的栅极。而栅极宽度越小,意味着闸门通道越小,那么单位面积所容纳的晶体管就会越多,芯片性能也就越强,芯片也就越先进。

我们以5nm为例,工艺制程指的是芯片栅极宽度,这个宽度是5nm。缩小晶体管的目的主要有两点:一是,减少耗电量,从而达到降低芯片能耗的目的;二是,增加晶体管数量,从而达到增强芯片性能的目的。

那么要缩小芯片哪一部分,才能达到这样的效果呢?答案仍然是栅极。

栅极:当晶体管工作时候,电流从漏极流向源极,但是受到一道阀门的控制,这道闸门就是栅极。而我们常说的7nm、5nm就是这道闸门的宽度,也就是栅极的宽度。通过缩小栅极宽度,从而达到降低芯片能耗、增强芯片性能。

因此,我们常说的7nm、5nm指的并不是晶体管的长度、宽度,而是说的栅极宽度。

芯片制造商为了升级芯片性能,也就把栅极宽度做的越窄,也就是纳米级别越小,芯片性能越先进。

纳米越小,芯片越先进吗?

纳米越小,芯片越先进吗?的确是

首先我们从理论上来分析:

缩小工艺制程有哪些好处呢?

1、降低能耗

缩小工艺制程后,晶体管之间的通道变窄,晶体管之间的电容也会变低,从而提升开关的频率。而晶体管开关消耗的电量与电容成正比,因此,电容降低后,开关速度更快、也更省电。

此外,工艺更精细的芯片,需要更低的开关电压,也能降低部分能耗。

2、节约材料

芯片向着更小的工艺尺寸进发,会导致组件更小,一片晶圆切割出来的芯片就会更多,进而节约材料,达到降低成本的目的。

但是,当芯片工艺达到一定程度后,尤其是进入7nm工艺后,高昂的设备成本、精细化制造、无尘化工厂等反而吞噬了晶圆切割出来的更多晶片。

3、满足轻薄设备的需求

缩小工艺尺寸还有一个好处,就是可以在不变大芯片的尺寸前提下,提高芯片能性能,以达到提高手机、电脑性能的目的。

同时高性能,小尺寸的芯片也有助于制造轻薄设备,使设备向轻薄型、微小型进军。

我们再用实例来对比:

1、麒麟970采用台积电10nm工艺制程,核心数量12,有55亿晶体管。

CPU:8核CPU,4个2.4GHz Cortex-A73核心+4个1.8GHz Cortex-A53核心;

GPU:12核,Mali-G72架构;

2、麒麟990采用台积电7nm工艺制程,核心数量16,有103亿晶体管,晶体管数量增加48亿个,约87%,较上一代芯片性能提升33%,能耗降低50%。

CPU:8核CPU,2个2.86GHz Cortex-A76核心+2个2.36GHz Cortex-A76核心+4个1.95GHz Cortex-A55核心;

GPU:12核,Mali-G76架构;

NPU::自研的达芬奇架构NPU,双大核 NPU +微核 NPU。

3、麒麟9000采用台积电5nm工艺制程,有194亿晶体管,晶体管数量增加91亿个,约88%,较上一代芯片性能提升50%,功耗降低30%。

CPU:8核CPU,2个3.13GHz Cortex-A76核心+2个2.54GHz Cortex-A76核心+4个2.05GHz Cortex-A55核心;

GPU:24核,Mali-G76架构;

NPU::双大核 NPU +微核 NPU。

通过对比,我们可以看出工艺制程越小,芯片越先进。晶体管数量更多、CPU性能更高、核心数也越多、最终提高了芯片的整体性能。

我们再来看这几款芯片搭载的手机跑分如何?

- 搭载麒麟970处理器的华为Mate10在安兔兔的成绩,跑分达到了21万分;

- 搭载麒麟990处理器的华为Mate30在安兔兔的成绩,跑分达到了42.6万分;

- 搭载麒麟9000处理器的华为Mate40在新版安兔兔的成绩,跑分达到了69万分。

跑分软件通过获得精准的设备信息,如:CPU型号、频率,系统版本号等,获得单项或整体得分,并借此判断硬件的性能水准。

通过安兔兔跑分软件可以看出,芯片制造工艺导致手机性能相差巨大,芯片工艺越精细,芯片性能越好,手机性能也会越好。

芯片制程越小越先进,那么芯片制程的极限是多少纳米

首先来了解一下摩尔定律

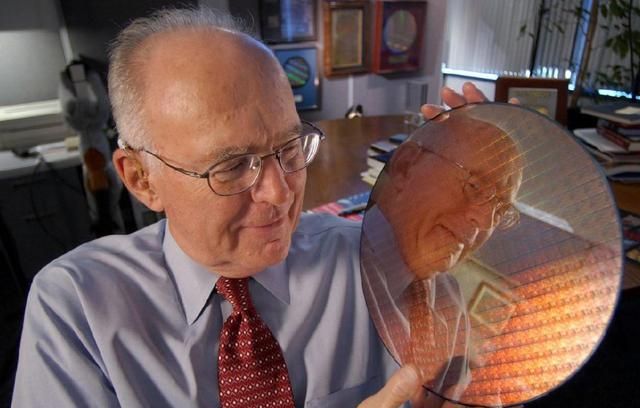

戈登 摩尔

摩尔定律:由英特尔创始人之一戈登摩尔提出,指的是当价格不变时,集成电路上可容纳的元器件的数目,约每隔18-24个月便会增加一倍,性能也将提升一倍。这一定律揭示了信息技术进步的速度。

摩尔定律对芯片制造业影响深远,在几十年的发展过程中,芯片开发商一直按照这个定律在逐步迭代芯片,从10微米到1微米,再到90纳米,随后进入65纳米、45纳米、32纳米,到现在的量产5nm。芯片不断地迭代,那么究竟多少纳米,才是芯片制程的极限,才是芯片制造的天空呢?

曾经一度认为7nm是芯片的物理极限

7nm之所以被认为是芯片物理极限,是因为,当制程低于7nm时,晶体管非常集中,而且距离非常近,栅极的厚度也接近极限,因此容易产生量子隧穿效应,漏电率会大幅增加,如果无法控制漏电率,那么制造工艺将止步于此。

芯片制造过程中,光刻机所发出的极紫外光会存在衍射现象,导致光刻栅长并不十分均匀,同时,在制造过程中,离子注入、蚀刻、等离子冲洗、热处理等步骤,也会导致实际栅长不均匀。

因此,由于栅长不均匀的问题,就导致行业普遍认为7nm工艺就是芯片的物理极限。

7nm、5nm技术逐渐攻破

2019年8月,三星发布旗舰芯片Exynos 9825,标志着7nmEUV技术的成功。一个月后,苹果发布新机型,搭载的芯片采用了台积电7nm EUV技术。

2020年10月,苹果发布iPhone 12搭载了A14处理器,华为发布了Mate40搭载了麒麟9000处理器。这两款处理器均采用了5nm EUV技术。

也就是传统的硅材料,能够量产7nm、5nm制程的芯片。

各大厂商开始进军3nm、2nm工艺

2020年8月25日开幕的在台积电第26届技术研讨会上,台积电公布了更先进的3nm、4nm工艺,此外,台积电还正式宣布建设新的研发中心,预计将投入8000多名工程师的人力到一条先进工艺生产线上,着力攻克2nm工艺。

三星也宣布了3nm的芯片,采用GAAFET晶体管技术,芯片流片成功,接下来真正进入量产阶段了,不再是PPT,而是实实在在的芯片技术了。

而最近台积电又与台大、麻省理工合作,研究用二维材料结合,达到极低电阻,接近量子极限,最终挑战1nm工艺制程。

可以看出,台积电、三星这些大厂,通过改良技术,采用新材料,估计最终把硅基材料的芯片的工艺做到1nm。

只有采用新材料才能突破摩尔定律

很多时候,技术的突破都是由材料的突破开始的。钢铁的诞生,促进了人类工业的快速发展;砷化镓(GaAs)的诞生,极大的促进了LED屏的发展;提纯硅的诞生,极大的促进了芯片技术的发展。

而同样,芯片工艺再突破,需要进行一场材料革命。借助新材料技术,突破摩尔定律是未来可行的方法。而且,部分大厂和研究机构已经开始研究了,并且取得了部分进展。

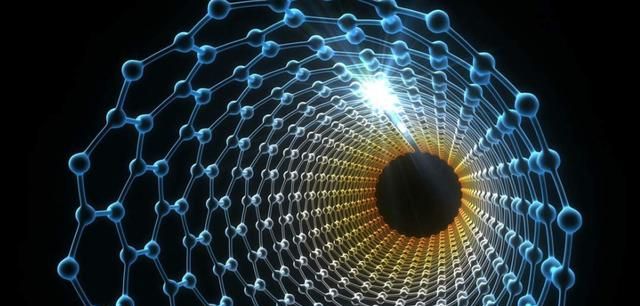

中国领先碳纳米管技术

2017年北京大学电子系教授兼中科院院士彭练矛团队成了碳纳米管,首次在实验上显示出碳纳米管器件和集成电路较传统技术的性能优势,2020年5月碳基芯片研究工作取得重大进展,并在国际顶级科学期刊《科学》上发表了成果。

碳纳米管具有多方面优势:

综合性能10倍领先于同时期性能最优的硅基晶体管;其工作速度3倍于英特尔最先进的14nm商用硅材料晶体管,能耗只有硅晶体管四分之一。

碳纳米管的成本低,而且尺寸小,只有1-3nm,更适合做小尺寸芯片,且强度高于钢铁,并具有弹性,可以做折叠芯片,也可以制作透明芯片等。

碳基芯片也有它的不足之处:

首先制作工艺落后硅基芯片,制程上远不如硅基芯片,制作工艺难度更大,碳纳米管需要提纯到99.9999%才可以制作芯片,而目前试剂公司只能提纯到99.99%。

除了碳纳米管外,氮化镓和碳化硅、二硫化钼、硅烯也被称为下一代芯片材料。

- GaN、SiC(氮化镓和碳化硅),这两种新型材料已经在芯片领域开始应用了,并且具有宽禁带、高热导率、高击穿电场、高抗辐射能力等特点;

- 二硫化钼(MoS2),二硫化钼已经在实验室中诞生了,而且1纳米工艺制程中表现不俗;

- 硅烯,硅和碳具有相似的化学性质,研究人员推测硅原子也可以像石墨烯那样,原子呈蜂窝状排列,形成硅烯这种物质。与石墨烯的重要不同在于,硅烯拥有可以实现逻辑电路所必要的能隙,但是硅烯最大的缺点就是不稳定,而且保存时间也短。

未来芯片能否突破1nm工艺制程,进入全新赛道,必须依靠新材料技术,如:碳纳米管、氮化镓和碳化硅、二硫化钼、硅烯。

问答总结

芯片单位纳米,并非是晶体管长度,而是晶体管中的栅极宽度。

无论是理论上,还是实际情况,芯片工艺制程越小,芯片越先进,性能越好。

常用的硅基芯片极限工艺制程是1nm—3nm,如果要突破这个极限,即必须要采用新材料,例如:碳纳米管、氮化镓和碳化硅、二硫化钼、硅烯。

我是科技铭程,以上是我的回答,希望可以帮到您,如有不妥之处,敬请批评指正!

高端芯片在宣传的时候,都会宣传其工艺制程是多少纳米的,比如高通骁龙855和华为海思麒麟985都是7nm的工艺制程。这种工艺制程是由光刻机来实现的,而纳米本身是一种长度单位,纳米数体现了芯片工艺制程水平的高低。

1 芯片的纳米是什么意思

芯片制造中,一项重要的工艺流程就是蚀刻,该工艺是由光刻机来实现的,纳米数就代表了蚀刻尺寸,表示晶体管之间的最小距离或者一个单位的集体管能蚀刻在硅片上的最小尺寸。纳米数越小,代表工艺水平越先进,代表单位面积内所能蚀刻的晶体管也就越多。目前,台积电和三星能实现7nm的EUV蚀刻技术,而且已经量产,台积电的下一代5nm的蚀刻技术正在建厂。高端芯片的制造只有几家企业可以实现,如台积电、三星、英特尔等。

2 纳米是什么单位

纳米nm跟米m、厘米cm一样是一个长度单位,只不过这个单位非常小。我们知道1米等于100厘米等于1000毫米,而纳米代表的是10的负9次方米。人体头发的直径一般在80微米左右,而1微米等于1000纳米,纳米单位是微米单位的千分之一。可见,纳米的单位有多小。

3 纳米数越小工艺制程越先进

毋庸置疑,芯片的纳米数越小越先进。纳米数越小,所需要的光刻机的蚀刻水平越高,那么单位面积内所能蚀刻的晶体管数量也就越多。同样体积大小的芯片,纳米数越小,代表内含的集体管数量也就越多、运算单元也就越多、性能也就越强劲、功耗也就越低。现在的产品都向着小型化、微型化去发展,而性能越来越强劲,这就对芯片的工艺制程提出了更高的要求。

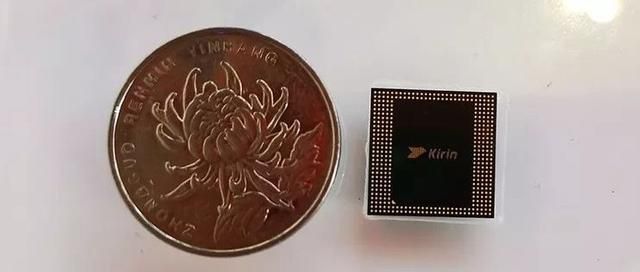

海思麒麟990 5G SOC就集成了103亿颗晶体管,而芯片本身还没有一枚硬币大。可见,芯片的蚀刻技术具有多高的技术含量。

以上就是的回答,如果您有其他的观点,可以在评论区留言讨论,如果您想获取更多的科技方面的前言技术,可以关注本头条号:玩转嵌入式。如果文章对您有所帮助,希望您点个赞转发一下。谢谢。

版权声明:本文来自用户投稿,不代表【闪电鸟】立场,本平台所发表的文章、图片属于原权利人所有,因客观原因,或会存在不当使用的情况,非恶意侵犯原权利人相关权益,敬请相关权利人谅解并与我们联系(邮箱:dandanxi6@qq.com)我们将及时处理,共同维护良好的网络创作环境。